1

Digital signal processor fundamentals and system design

M.E. Angoletta

CERN, Geneva, Switzerland

Abstract

Digital Signal Processors (DSPs) have been used in accelerator systems for

more than fifteen years and have largely contributed to the evolution towards

digital technology of many accelerator systems, such as machine protection,

diagnostics and control of beams, power supply and motors. This paper aims

at familiarising the reader with DSP fundamentals, namely DSP

characteristics and processing development. Several DSP examples are

given, in particular on Texas Instruments DSPs, as they are used in the DSP

laboratory companion of the lectures this paper is based upon. The typical

system design flow is described; common difficulties, problems and choices

faced by DSP developers are outlined; and hints are given on the best

solution.

1 Introduction

1.1 Overview

Digital Signal Processors (DSPs) are microprocessors with the following characteristics:

a) Real-time digital signal processing capabilities. DSPs typically have to process data in real

time, i.e., the correctness of the operation depends heavily on the time when the data

processing is completed.

b) High throughput. DSPs can sustain processing of high-speed streaming data, such as audio

and multimedia data processing.

c) Deterministic operation. The execution time of DSP programs can be foreseen accurately,

thus guaranteeing a repeatable, desired performance.

d) Re-programmability by software. Different system behaviour might be obtained by

re-coding the algorithm executed by the DSP instead of by hardware modifications.

DSPs appeared on the market in the early 1980s. Over the last 15 years they have been the key

enabling technology for many electronics products in fields such as communication systems,

multimedia, automotive, instrumentation and military. Table 1 gives an overview of some of

these fields and of the corresponding typical DSP applications.

Figure 1 shows a real-life DSP application, namely the use of a Texas Instruments (TI) DSP in a

MP3 voice recorder–player. The DSP implements the audio and encode functions. Additional tasks

carried out are file management, user interface control, and post-processing algorithms such as

equalization and bass management.

167

2

Table 1: A short selection of DSP fields of use and specific applications

Field

Application

Video conferencing / phone

Voice / multimedia over IP

Broadband

Digital media gateways (VOD)

Satellite phone

Communication

Wireless

Base station

Biometrics

Security

Video surveillance

Digital still /video camera

Digital radio

Entertainment

Portable media player / entertainment console

Interactive toys

Consumer

Toys

Video game console

MRI

Ultrasound

Medical

X-ray

Scanner

Point of sale

Vending machine

Factory automation

Industrial / machine / motor control

Industrial and

entertainment

Industrial

Vision system

Guidance (radar, sonar)

Avionics

Digital radio

Military and aerospace

Smart munitions, target detection

M.E. ANGOLETTA

168

3

Fig. 1: Use of Texas Instruments DSP in a MP3 player/recorder system. Picture courtesy of

Texas Instruments from www.ti.com.

1.2 Use in accelerators

DSPs have been used in accelerators since the mid-1980s. Typical uses include diagnostics, machine

protection and feedforward/feedback control. In diagnostics, DSPs implement beam tune, intensity,

emittance and position measurement systems. For machine protection, DSPs are used in beam current

and beam loss monitors. For control, DSPs often implement beam controls, a complex task where

beam dynamics plays an important factor for the control requirements and implementations. Other

types of control include motor control, such as collimation or power converter control and regulation.

The reader can find more information on DSP applications to accelerators in Refs. [1–3].

DSPs are located in the system front-end. Figure 2 shows CERN’s hierarchical controls

infrastructure, a three-tier distributed model providing a clear separation between Graphical User

Interface (GUI), server, and device (front-end) tiers.

DSPs are typically hosted on VME boards which can include one or more programmable

devices such as Complex Programmable Logic Devices (CPLDs) or Field Programmable Gate Arrays

(FPGAs). Daughtercards, indicated in Fig. 2 as dashed boxes, are often used; their aim is to construct a

system from building blocks and to customize it by different FPGA/DSP codes and by the

daughtercards type. DSPs and FPGAs are often connected to other parts of the system via low-latency

data links. Digital input/output, timing, and reference signals are also typically available. Data are

exchanged between the front-end computer and the DSP over the VME bus via a driver.

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

169

4

Fig. 2: Typical controls infrastructure used at CERN and DSP characteristics location

2 DSP evolution and current scenery

DSPs appeared on the market in the early 1980s. Since then, they have undergone an intense evolution

in terms of hardware features, integration, and software development tools. DSPs are now a mature

technology. This section gives an overview of the evolution of the DSP over their 25-year life span;

specialized terms such as ‘Harvard architecture’, ‘pipelining’, ‘instruction set’ or ‘JTAG’ are used.

The reader is referred to the following paragraphs for explanations of their meaning. More detailed

information on DSP evolution can be found in Refs. [4], [5].

2.1 DSP evolution: hardware features

In the late 1970s there were many chips aimed at digital signal processing; however, they are not

considered to be digital signal processing owing to either their limited programmability or their lack of

hardware features such as hardware multipliers. The first marketed chip to qualify as a programmable

DSP was NEC’s MPD7720, in 1981: it had a hardware multiplier and adopted the Harvard

architecture (more information on this architecture is given in Section 3.1). Another early DSP was the

TMS320C10, marketed by TI in 1982. Figure 3 shows a selective chronological list of DSPs that have

been marketed from the early 1980s until now.

From a market evolution viewpoint, we can divide the two and a half decades of DSP life span

into two phases: a development phase, which lasted until the early 1990s, and a consolidation phase,

lasting until now. Figure 3 gives an overview of the evolution of DSP features together with the first

year of marketing for some DSP families.

M.E. ANGOLETTA

170

5

Fig. 3: Evolution of DSP features from their early days until now. The first year of marketing

is indicated at the top for some DSP families.

During the market development phase, DSPs were typically based upon the Harvard

architecture. The first generation of DSPs included multiply, add, and accumulator units. Examples are

TI’s TMS320C10 and Analog Devices’ (ADI) ADSP-2101. The second generation of DSPs retained

the architectural structure of the first generation but added features such as pipelining, multiple

arithmetic units, special address generator units, and Direct Memory Access (DMA). Examples

include TI’s TMS320C20 and Motorola’s DSP56002. While the first DSPs were capable of fixed-

point operations only, towards the end of the 1980s DSPs with floating point capabilities started to

appear. Examples are Motorola’s DSP96001 and TI’s TMS320C30. It should be noted that the

floating-point format was not always IEEE-compatible. For instance, the TMS320C30 internal

calculations were carried out in a proprietary format; a hardware chip converter [6] was available to

convert to the standard IEEE format. DSPs belonging to the development phase were characterized by

fixed-width instruction sets, where one of each instruction was executed per clock cycle. These

instructions could be complex, and encompassing several operations. The width of the instruction was

typically quite short and did not overcome the DSP native word width. As for DSP producers, the

market was nearly equally shared between many manufacturers such as AT&T, Fujitsu, Hitachi, IBM,

NEC, Toshiba, Texas Instruments and, towards the end of the 1980s, Motorola, Analog Devices and

Zoran.

During the market consolidation phase, enhanced DSP architectures such as Very Long

Instruction Word (VLIW) and Single Instruction Multiple Data (SIMD) emerged. These architectures

increase the DSP performance through parallelism. Examples of DSPs with enhanced architectures are

TI’s TMS320C6xxx DSPs, which was the first DSP to implement the VLIW architecture, and ADI’s

TigerSHARC, that includes both VLIW and SIMD features. The number of on-chip peripherals

increased greatly during this phase, as well as the hardware features that allow many processors to

work together. Technologies that allow real-time data exchange between host processor and DSP

started to appear towards the end of the 1990s. This constituted a real sea change in DSP system

debugging and helped the developers enormously. Another phenomenon observed during this phase

was the reduction of the number of DSP manufacturers. The number of DSP families was also greatly

reduced, in favour of wider families that granted increased code compatibility between DSPs of

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

171

6

different generations belonging to the same family. Additionally, many DSP families are not ‘general-

purpose’ but are focused on specific digital signal processing applications, such as audio equipment or

control loops.

2.2 DSP evolution: device integration

Table 2 shows the evolution over the last 25 years of some key device characteristics and their

expected values after the year 2010.

Table 2: Overview of DSP device characteristics as a function of time. The last column refers

to expected values.

Year

Characteristic

1980

1990

2000

> 2010

Wafer size [inches]

3

6

12

18

Die size [mm]

50

50

50

5

Feature [µm]

3

0.8

0.1

0.02

RAM [Bytes]

256

2000

32000

1 million

Clock frequency [MHz]

20

80

1000

10000

Power [mW/MIPS]

250

12.5

0.1

0.001

Price [USD]

150

15

5

0.15

Wafer, die, and feature sizes are the basic key factors that define a chip technology. The wafer

size is the diameter of the wafer used in the semiconductor manufacturing process. The die size is the

size of the actual chips carved up in a wafer. The feature size is the size of the smallest circuit

component (typically a transistor) that can be etched on a wafer; this is used as an overall indicator of

the density of an Integrated Circuit (IC) fabrication process. The trend in industry is to go towards

larger wafers and chip dies, so as to increase the number of working chips that can be obtained from

the same wafer; also called yield. For instance, the current typical wafer size is 12 inches (300 mm),

and some leading chip maker companies plan to move to 18 inches (450 mm) within the first half of

the next decade. (It should be added that the issue is somewhat controversial, as many equipment

manufacturers fear that the 18 inches wafer size will lead to scale problems even worse than for the

12 inches.) Feature size is decreasing, allowing one to either have more functionality on a die or to

reduce the die size while keeping the same functionality. Transistors with smaller sizes require less

voltage to drive them; this results in a decrease of the core voltage from 5 V to 1.5 V. The I/O voltage

has been lowered as well, with the caveat that it remains compatible with the external devices used and

their standard. A lower core voltage has been one of the key factors enabling higher clock frequencies:

in fact, the gap between high and low state thresholds is tightened thus allowing a faster logic level

transition. Additionally, the reduced die size and lowered core voltage allow lower power

consumption, an important factor for portable or mobile system. Finally, the global cost of a chip has

decreased by at least a factor 30 over the last 25 years.

The trend towards a faster switching hardware (including chip over-clocking) and smaller

feature size carries the benefit of increased processing power and throughput. There is a downside to

it, however, represented by the electromigration phenomenon. Electromigration occurs when some of

the momentum of a moving electron is transferred to a nearby activated ion, hence causing the ion to

move from its original position. Gaps or, on the contrary, unintended electrical connections can

develop with time in the conducting material if a significant number of atoms are moved far from their

M.E. ANGOLETTA

172

7

original position. The consequence is the electrical failure of the electronic interconnects and the

consequent shortened chip lifetime.

2.3 DSP evolution: software tools

The improvement of DSP software tools from the early days until now has been spectacular.

Code compilers have evolved greatly to be able to deal with the underlying hardware

complexity and the enhanced DSP architectures. At the same time, they allow the developer to

program more and more efficiently in high-level languages as opposed to assembly coding. This

speeds up considerably the code development time and makes the code itself more portable across

different platforms.

Advanced tools now allow the programming of DSPs graphically, i.e., by interconnecting

pre-defined blocks that are then converted to DSP code. Examples of these tools are MATLAB Code

Generation and embedded target products and National Instruments' LabVIEW DSP Module.

High-performance simulators, emulator and debugging facilities allow the developer to have a

high visibility into the DSP with little or no interference on the program execution. Additionally,

multiple DSPs can be accessed in the same JTAG chain for both code development and debugging.

2.4 DSP current scenery

The number of DSP vendors is currently somewhat limited: Analog Devices (ADI), Freescale

(formerly Motorola), Texas Instruments (TI), Renesas, Microchip and VeriSilicon are the basic

players. Amongst them, the biggest share of the market is taken by only three vendors, namely ADI,

TI and Freescale. In the accelerator sector one can find mostly ADI and TI DSPs, hence most of the

examples in this document will be focused on them. Table 3 lists the main DSP families for ADI and

TI DSPs, together with their typical use and performance.

Table 3: Main ADI and TI DSP families, together with their typical use and performance

Manufacturer

Family

Typical use and performance

TMS320C2x

Digital signal controllers

TMS320C5x

Power efficient

TI

TMS320C6x

High performance

SHARC

Medium performance. First ADI family (now three generations)

TigerSHARC

High performance for multi-processor systems

ADI

Blackfin

High performance and low power

3 DSP core architecture

3.1 Introduction

DSP architecture has been shaped by the requirements of predictable and accurate real-time digital

signal processing. An example is the Finite Impulse Response (FIR) filter, with the corresponding

mathematical equation (1), where y is the filter output, x is the input data and a is a vector of filter

coefficients. Depending on the application, there might be just a few filter coefficients or many

hundreds or more.

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

173

8

!

=

"#=

M

k

k

knxany

0

)()(

.

(1)

As shown in Eq. (1), the main component of a filter algorithm is the ‘multiply and accumulate’

operation, typically referred to as MAC. Coefficients data have to be retrieved from the memory and

the whole operation must be executed in a predictable and fast way, so as to sustain a high throughput

rate. Finally, high accuracy should typically be guaranteed. These requirements are common to many

other algorithms performed in digital signal processing, such as Infinite Impulse Response (IIR) filters

and Fourier Transforms. Table 4 shows a selection of processing requirements together with the main

DSP hardware features satisfying them. These hardware features are discussed in more detail in

Sections 3.2 to 3.5 and a full overview of a typical DSP core will be built step by step (see Figs. 4, 7,

10, 13). More detailed information on DSP architectural features can be found in Refs. [7] –[14].

Table 4: Main requirements and corresponding DSP hardware implementations for predictable

and accurate real-time digital signal processing. The numbers in the first column refer to the section

treating the topic.

Processing requirements

Hardware implementations satisfying the requirement

3.2 Fast data access

• High-bandwidth memory architectures

• Specialized addressing modes

• Direct Memory Access (DMA)

3.3 Fast computation

• MAC-centred

• Pipelining

• Parallel architectures (VLIW, SIMD)

3.4 Numerical fidelity

• Wide accumulator registers, guard bits, etc.

3.5 Fast execution control

• Hardware-assisted, zero-overhead loops, shadow registers, etc.

3.2 Fast data access

Fast data access refers to the need of transferring data to / from memory or DSP peripherals, as well as

retrieving instructions from memory. The hardware implementations considered for this are three,

namely a) high-bandwidth memory architectures, discussed in Sub-section 3.2.1; b) specialized

addressing modes, discussed in Sub-section 3.2.2; c) direct memory access discussed in

Sub-section 3.2.3.

3.2.1 High-bandwidth memory architectures

Traditional general-purpose microprocessors are based upon the Von Neumann architecture, shown in

Fig. 4(a). This consists of a single block of memory, containing both data and program instructions,

and of a single bus (called data bus) to transfer data and instructions from/to the CPU. The

disadvantage of this architecture is that only one memory access per instruction cycle is possible, thus

constituting a bottleneck in the algorithm execution.

DSPs are typically based upon the Harvard architecture, shown in Fig. 4(b), or upon modified

versions of it, such as the Super-Harvard architecture shown in Fig. 4(c). In the Harvard architecture

there are separate memories for data and program instructions, and two separate buses connect them to

the DSP core. This allows fetching program instructions and data at the same time, thus providing

better performance at the price of an increased hardware complexity and cost. The Harvard

M.E. ANGOLETTA

174

9

architecture can be improved by adding to the DSP core a small bank of fast memory, called

‘instruction cache’, and allowing data to be stored in the program memory. The last-executed program

instructions are relocated at run time in the instruction cache. This is advantageous for instance if the

DSP is executing a loop small enough so that all its instructions can fit inside the instruction cache: in

this case, the instructions are copied to the instruction cache the first time the DSP executes the loop.

Further loop iterations are executed directly from the instruction cache, thus allowing data retrieval

from program and data memories at the same time.

Fig. 4: (a) Von Neumann architecture, typical of traditional general-purpose microprocessors.

(b) Harvard and (c) Super-Harvard architectures, typical of DSPs.

Another more recent improvement of the Harvard architecture is the presence of a ‘data cache’,

namely a fast memory located close to the DSP core which is dynamically loaded with data. Of course,

the fact of having the cache memory very close to the DSP allows clocking it at high speed, as routing

wire delays are short. Figure 5 shows the cache architecture for TI TMS320C67xx DSP, including

both program and data cache. There are two levels of cache, called Level 1 (L1) and Level 2 (L2). The

L1 cache comprises 8 kbyte of memory divided into 4 kbyte of program cache and 4 kbyte of data

cache. The L2 cache comprises 256 kbyte of memory divided into 192 kbyte mapped-SRAM memory

and 64 kbyte dual cache memory. The latter can be configured as mapped memory, cache or a

combination of the two. The reader can find more information on TI TMS320C67xx DSP two-level

memory architecture and configuration possibilities in Ref. [12].

Fig. 5: TI DSP TMS320C67xx family two-level cache architecture

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

175

10

Figure 6 shows the hierarchical memory architecture to be found in a modern DSP [13]. Typical

levels of memory and corresponding access time, hardware implementation, and size are also shown.

As remarked above, a hierarchical memory allows one to take advantage of both the speed and the

capacity of different memory types. Registers are banks of very fast internal memory, typically with

single-cycle access time. They are a precious DSP resource used for temporary storage of coefficients

and intermediate processing values. The L1 cache is typically high-speed static RAM made of five or

six transistors. The amount of L1 cache available thus depends directly on the available chip space. A

L2 cache needs typically a smaller number of transistors hence can be present in higher quantities

inside the DSPs. Recent years have also seen the integration of DRAM memory blocks into the DSP

chip [14], thus guaranteeing larger internal memories with relatively short access times. The Level 3

(L3) memory shown in Fig. 6 is rarely present in DSPs while the external memory is typically

available. This is often a large memory with long access times.

Fig. 6: DSP hierarchical memory architecture and typical number of access clock cycles, hardware

implementation, and size for different memory types

As shown above, cache memories improve the average system performance. However, there are

drawbacks to the presence of a cache in DSP-based systems, owing to the lack of full predictability for

cache hits. A missing cache hit happens when the data or the instructions needed by the DSP are not

stored in cache memory, hence they have to be fetched from a slower memory with an execution speed

penalty. A situation causing a missing cache hit is, for instance, the flow change due to branch

instructions. The consequence is a difficult worst-case-scenario prediction, which is particularly

negative for DSP-based systems where it is important to be able to calculate and predict the system

time response. There may, however, be methods used to limit these effects, such as the possibility for

the user to lock the cache so as to execute time-critical sections in a deterministic way. Advanced

cache organizations characterized by a uniform memory addressing are also under study [15].

3.2.2 Specialized addressing modes

DSPs include specialized addressing modes and corresponding hardware support to allow a rapid

access to instruction operands through rapid generation of their location in memory. DSPs typically

support a wide range of specialized addressing modes, tailored for an efficient implementation of

digital signal processing algorithms.

Figure 7 adds the address generator units to the basic DSP architecture shown in Fig. 4(c). As in

general-purpose processors, DSPs include a Program Sequencer block, which manages program

structure and program flow by supplying addresses to memory for instruction fetches. Unlike general-

purpose processors, DSPs include address generator blocks, which control the address generation for

specialized addressing modes such as indexing addressing, circular buffers, and bit-reversal

addressing. The two last addressing modes are discussed below.

M.E. ANGOLETTA

176

11

Fig. 7: Program sequencer and address generator units location within a generic DSP core

architecture

Circular buffers are limited memory regions where data are stored in a First-In First-Out (FIFO)

way; these memory regions are managed in a ‘wrap-around’ way, i.e., the last memory location is

followed by the first memory location. Two sets of pointers are used, one for reading and one for

writing; the length of the step at which successive memory locations are accessed is called ‘stride’.

Address generator units allow striding through the circular buffers without requiring dedicated

instructions to determine where to access the following memory location, error detection and so on.

Circular buffers allow storing bursts or continuous streams of data and processing them in the order in

which they have arrived. Circular buffers are used for instance in the implementation of digital filters;

strides higher than one are useful in case of multi-rate signal processing. Figure 8 shows the order in

which data are accessed for a read operation in case of an eleven-element circular buffer and with a

stride equal to four.

Fig. 8: Example of read data access order in a circular buffer composed of 11 elements and with

stride equal to 4 elements

Bit-reversal addressing, shown in Fig. 9, is an essential step in the discrete Fourier transforms

calculation. In fact, many implementations of the Fourier transforms require a re-ordering of either the

input or the output data that corresponds to reversing the order of the bits in the array index. Figure 9

gives an example of the bit-reversal mechanism. Carrying it out by software is very demanding and

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

177

12

would result in using many CPU cycles, which are saved thanks to the hardware bit-reversal

functionality.

Fig. 9: Bit-reversal mechanism

3.2.3 Direct Memory Access (DMA) controller

The DMA controller is a second processor working in parallel with the DSP core and dedicated to

transferring information between two memory areas or between peripherals and memory. In doing so

the DMA controller frees the DSP core for other processing tasks. Figure 10 shows an example of the

DMA location within a general DSP core architecture.

Fig. 10: An example of DMA controller location within a generic DSP core architecture

A DMA coprocessor can transfer data as well as program instructions, the latter transfer

corresponding typically to the case of code overlay, i.e., of code stored in an external memory and

moved to an internal memory (for instance L1) when needed. Multiple and independent DMA

channels are also available for greater flexibility. Bus arbitration between the DMA and the DSP core

is needed to avoid colliding memory accesses when the DMA and the DSP core share the same bus to

access peripherals and/or memories. To prevent bottlenecks, recent DSPs typically fit DMA

controllers with dedicated buses.

M.E. ANGOLETTA

178

13

Figure 11 shows the advantages of DMA for the DSP core efficient use: the DSP core must set

up the DMA but still there is a net gain in the DSP core availability for other processing activities.

Nowadays there are two classes of DMA transfer configurations: register-based and RAM-based, the

latter one also called descriptor-based. In register-based DMA controllers the transfer set-up is done by

the DSP core via the registers set-up. This method is very efficient but allows mainly simple DMA

operations. In RAM-based DMA controllers the set-up parameters are stored in memory. This method

is preferred by powerful and recent DSPs as it allows great DMA transfer flexibility.

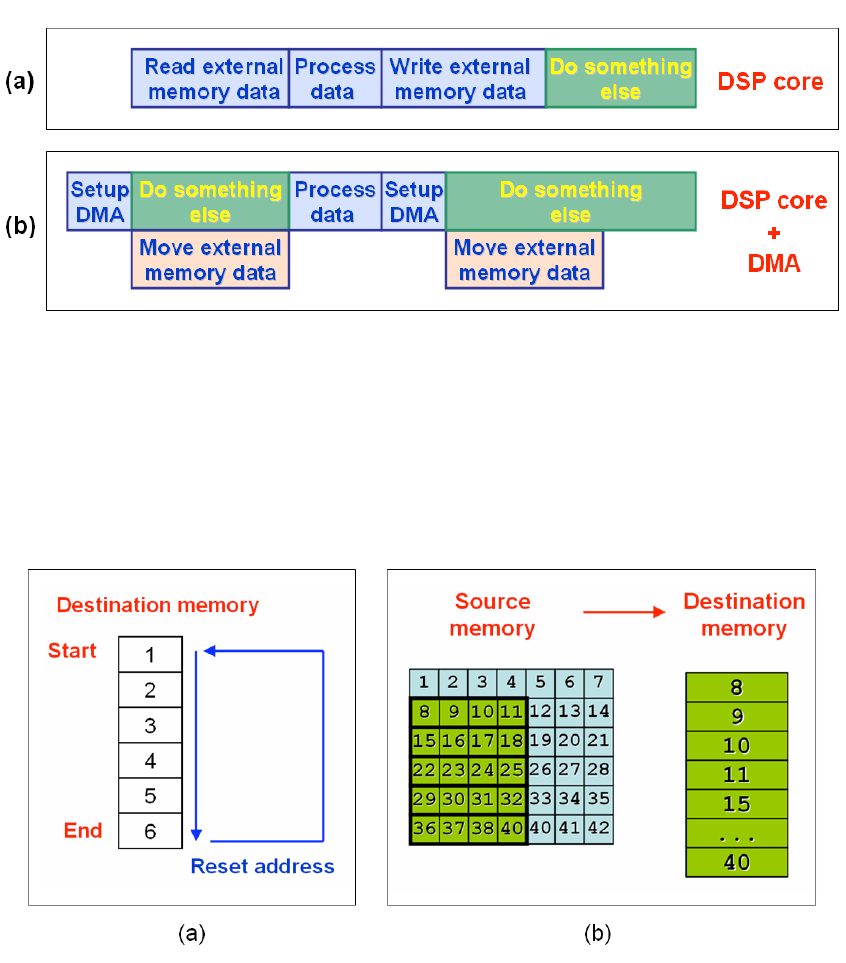

Fig. 11: (a) Read–process–write data when the DSP core only is present; (b) same activity when

the DMA takes care of data transfers

Figure 12 provides two examples of transfer configurations. Plot (a) shows a chained DMA

transfer, where the completion of a data transfer triggers a new transfer. This type of data transfer is

particularly suited to applications that require a continuous data stream in input. Plot (b) shows a

multi-dimensional data transfer, obtained by changing the stride of the DMA transfer. This type of

data transfer is particularly useful for video applications.

Fig. 12: Examples of DMA transfer configurations. (a): chained DMA transfer; (b): Multi-

dimensional data transfer.

DSP external events and interrupts can be used to trigger a DMA data transfer. DMA controllers

can also generate interrupts to communicate with the DSP core, for instance to inform it that a data

transfer has been completed. An example of a powerful and highly flexible DMA controller is that

implemented for TI’s TMS320C6000 family [16].

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

179

14

3.3 Fast computation

Here we discuss techniques and architectures used in DSPs for a fast computation. The MAC-centred

architecture described in Sub-section 3.3.1 has been common to all DSPs since their early days. The

techniques and architectures described in Sub-sections 3.3.2 and 3.3.3 were introduced from the 1990s

onwards.

3.3.1 MAC-centred

The MAC operation is used by many digital processing algorithms, as discussed at the beginning of

Section 3; consequently its execution must be optimized so as to improve the DSP overall

performance. The basic DSP arithmetic processing blocks are a) many registers; b) one or more

multipliers; c) one or more Arithmetic Logic Units (ALUs); d) one or more shifters. These blocks

work in parallel during the same clock cycle thus optimizing MAC as well as other arithmetic

operations. The blocks are shown in Fig. 13 and are briefly described below.

a) Registers: these are banks of very fast memory used to store intermediate data processing.

Very often they are wider than the DSP normal word width, so as to provide a higher

resolution during the processing.

b) Multiplier: it can carry out single-cycle multiplications and very often it includes very wide

accumulator registers to reduce round-off or truncation errors. As a consequence, truncation

and round-off errors will happen only at the end of the data processing, when the data is

stored onto memory. Sometimes an adder is integrated in the multiplier unit.

c) ALU: it carries out arithmetic and logical operations.

d) Shifters: it shifts the input value by one or more bits, left or right. In the latter case, the

shifter is called a barrel shifter and is especially useful in the implementation of floating

point add and subtract operations.

Fig. 13: Basic DSP arithmetic processing blocks. The structure shown is that of ADI SHARC.

M.E. ANGOLETTA

180

15

3.3.2 Instruction pipelining

Instruction pipelining has become an important element to achieve high DSP performance. It consists

of dividing the execution of instructions into different stages and executing the different instructions in

parallel stages. The net result is an increased throughput of the instruction execution. The whole

process can be compared to a factory assembly line, which produces cars for instance: more than one

car is in the assembly line at the same moment, at different stages of assembly. This provides a

production higher than the case where only one car at a time is produced, where many specialized

crews are idle waiting for the next car to require their work.

Table 5 shows the basic pipelining stage into which each instruction is divided:

1. Fetch. The DSP calculates the address of the next instruction to execute and retrieve the op-

code, i.e., the binary word containing the operands and the operation to be carried out on them.

2. Decode. The op-code is interpreted and sent to the corresponding functional unit. The

instruction is interpreted and the operands are retrieved.

3. Execute. The instruction is executed and the results are written onto the registers.

Table 5: The three basic pipelining stages and corresponding actions

Basic pipelining stages

Action

Fetch

• Generate program fetch address

• Read op-code

Decode

• Route op-code to functional unit

• Decode instruction

• Read operands

Execute

• Execute instruction

• Write results back to registers

Figure 14 shows the advantage of a pipelined CPU with respect to a non-pipelined CPU, in

terms of processing time gain. In a non-pipelined CPU the different instructions are executed serially,

while in a pipelined CPU only the same type of stages (e.g. Fetch, Decode and Execute) are serialized

and different instructions are executed in parallel. A pipeline is called fully-loaded if all stages are

executed at the same time; this corresponds to the maximum possible instruction throughput. The

depth of the pipeline, i.e., the number of stages into which an instruction is divided, can vary from one

processor to another. Generally speaking a deeper pipeline allows the processor to execute faster,

hence many processors sub-divide pipeline stages into smaller steps, each one executed at each clock

cycle. The smaller the step, the faster the processor clock speed can be. An example of deep pipeline is

the TI TMS320C6713 DSP, which includes four fetch stages, two decode stages, and up to ten

execution stages.

There are drawbacks and limitations to the pipelining technique. One drawback is the hardware

and programming complexity required by it, for instance in terms of capabilities needed in the

compiler and the scheduler. This is especially true in the case of deep pipelines. A limitation in the

effective instruction execution throughput is given by situations that prevent the pipeline from being

fully-loaded. These situations include pipeline flushes due to changes in the program flow, such as

code branches or interrupts. In this case, the DSP does not know which instructions it should execute

next until the branch instruction is executed. Other situations are data hazards, namely when one

instruction needs the result of a previous instruction to be executed. Apart from a reduced throughput,

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

181

16

Fig. 14: Instruction execution and processing time gain of a pipelined CPU (plot b) with respect to

a non-pipelined one (plot a)

these pipeline limitations cause a more difficult prediction of the worst-case scenario. Techniques not

described here are available to provide the DSP programmer with a pipeline control; they include

time-stationary pipeline control, data-stationary control, and interlocked pipeline.

3.3.3 Parallel architectures

The DSP performance can be increased by an increased parallelism in the instructions execution.

Parallel-enhanced DSP architectures started to appear on the market in the mid 1990s and were based

on instruction-level parallelism, data-level parallelism, or a combination of both. These two

approaches are called Very Long Instruction Word (VLIW) and Single-Input Multiple-Data (SIMD),

respectively and are discussed below. The reader is referred to Refs. [17] and [18] for more

information on the subject.

VLIW architectures are based upon instruction level parallelism, i.e., many instructions are

issued at the same time and are executed in parallel by multiple execution units. As a consequence,

DSPs based on this architecture are also called ‘multi-issue’ DSP. This is an innovative architecture

that was first used in the TI TMS320C62xx DSP family. Figure 15 shows an example of the VLIW

architecture: eight, 32-bit instructions are packed together in a 256-bit wide instruction which is fed to

eight separate execution units. Characteristics of VLIW architectures include simple and regular

instruction sets. Instruction scheduling is done at compile-time and not at run-time so as to guarantee a

deterministic behaviour. This means that the decision on which instructions have to be executed in

parallel is done when the program is compiled, hence the order does not change during the program

execution. A run-time scheduling would instead make the scheduling dependent on data and resources

availability, which could change for different program executions. An important advantage of the

VLIW architecture is that it can increase the DSP performance for a wide range of algorithms.

Additionally, the architecture is potentially scalable, i.e., more execution units could be added to allow

a higher number of instructions to be executed in parallel. There are disadvantages as well, such as the

high memory use and power consumption required by this architecture. From a programmer’s

viewpoint, writing assembly code for VLIW architecture is very complex and the optimization is often

better left to the compiler.

M.E. ANGOLETTA

182

17

Fig. 15: TI TMS320C6xxx family VLIW architecture

SIMD architectures are based on data-level parallelism, i.e., only one instruction is issued at a

time but the same operation specified by the instruction is performed on multiple data sets. Figure 16

shows the example of a DSP based upon the SIMD architecture: two 32-bit input registers provide

four, 16-bit each, data inputs. They are processed in parallel by two separate execution units that carry

out the same operation. The two, 16-bit data outputs are packed into a 32-bit register. Typical SIMD

architecture can support multiple data width and is most effective on algorithms that require the

processing of large data chunks. The SIMD operation mode can be switched ON or OFF, for instance

in the ADI SHARC DSP. An advantage of the SIMD architecture is that it is applicable to other

architectures; an example is the ADI TigerSHARC DSP that comprises both VLIW and SIMD

characteristics. SIMD drawbacks include the fact that SIMD architectures are not useful for algorithms

that process data serially or that contain tight feedback loops. It is sometimes possible to convert serial

algorithms to parallel ones; however, the cost is in reorganization penalties and in a higher program-

memory usage, owing to the need to re-arrange the instructions.

Fig. 16: Simplified schematics for ADI SHARC DSP as an example of SIMD architecture

3.4 Numerical fidelity

Arithmetic operations such as additions and multiplications are the heart of DSP systems. It is thus

essential that the numerical fidelity be maximized, i.e., that errors due to the finite number of bits used

in the number representation and in the arithmetic operations be minimized. DSPs have many ways to

obtain this, ranging from the numeric representation to dedicated hardware features.

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

183

18

As far as the number representation is concerned, DSPs can be divided into two categories:

fixed point and floating point.

Fixed-point DSPs perform integer as well as fractional arithmetic, and can support data widths

of 16, 24 or 32 bits. A fixed-point format can represent both signed and unsigned integers and

fractions. Fractional numbers can take values in the [−1.0, 1.0] range and are often indicated as Qx.y,

where ‘x’ indicates the number of bits located before the binary point and ‘y’ the number of bits after

it. Figure 17(a) shows how 16-bit signed fractional point numbers are coded. Signed fractional

numbers with 24-bit and 32-bit data width are coded in an equivalent way as Q1.23 and Q1.31,

respectively. They can take values in the same [−1.0, 1.0] range, however, their resolution is higher

than the 16-bit implementation. An example of extended precision fixed-point can be found in

Ref. [19].

Floating-point DSPs represent numbers with a mantissa and an exponent, nowadays following

the IEEE 754 [20] standard shown in Fig. 17(b) for a 32-bit number. The mantissa dictates the number

precision and the exponent controls its dynamic range. Numbers are scaled so as to use the full word-

length available, hence maximizing the attainable precision. The reader is referred to Ref. [21] for

more information on the subject.

Fig. 17: (a): 16-bit signed fractional point, often indicated as Q1.15. (b): IEEE 754 normalized

representation of a single precision floating point number.

Floating-point numbers provide a higher dynamic range, which can be essential when dealing

with large data sets and with data sets whose range cannot be easily predicted. The dynamic range for

a 32-bit number represented as fixed-point and as floating-point is shown in Fig. 18.

Fig. 18: Dynamic range for 32-bit data, represented as 32-bit signed fractional point and IEEE 754

normalized number

In addition to the different number formats available, DSPs provide hardware ways to improve

numerical fidelity. One example is represented by the large accumulator registers, used to hold

intermediate and final results of arithmetic operations. These registers are several bits (at least four)

wider than the normal registers in order to prevent overflow as much as possible during accumulation

operations. The extra bits are called guard bits and allow one to retain a higher precision in

M.E. ANGOLETTA

184

19

intermediate computation steps. Flags to indicate that an overflow/underflow has happened are also

available. These flags are often connected to interrupts, thus allowing exception-handling routines to

be called. Another means DSPs have to improve numerical fidelity is saturated arithmetic. This means

that a number is saturated to the maximum value that can be represented, so as to avoid wrap-around

phenomena.

3.5 Fast-execution control

Here we show two important examples of how DSP can fast-execute control instructions. The first

example is the zero-overhead hardware loop and refers to the program flow control in loops. The

second example refers to how DSPs react to interrupts.

Looping is a critical feature in many digital signal processing algorithms. An important DSP

feature is the implementation by hardware of looping constructs, referred to as ‘zero-overhead

hardware loop’. This allows DSP programmers to initialize loops by setting a counter and defining the

loop bounds, without spending any software overhead to update and test loop counters or branching

back to the beginning of the loop.

The capability to service interrupts very quickly and in a deterministic way is an important DSP

characteristic. Interrupts are internal (for instance generated by internal timers) or external (brought to

the DSP code via pins) events that change the DSP execution flow when they are serviced. The latency

is the time elapsed from when the interrupt event is triggered and when the DSP starts to execute the

first instruction of the corresponding Interrupt Service Routine (ISR). When an interrupt is received

and if the interrupt has a sufficiently-high priority, the DSP must carry out the following actions:

a) stop its current activity;

b) save the information related to the interrupted activity (called context) into the DSP stack;

c) start servicing the interrupt.

The context corresponding to the interrupted activity can be restored when the ISR has been

executed and the previous activity is continued.

Table 6: Interrupt dispatchers available on the ADI ADSP21160M DSP. The instruction cycle is 12.5 µs, hence

the number of cycles can easily be converted to time.

Interrupt dispatcher

Cycles before ISR

Cycles after ISR

Normal

183

109

Fast

40

26

Super-fast (with alternate registers set)

34

10

Final

24

15

More than one interrupt dispatcher is typically available in a DSP; this means that the user can

select the amount of context to be saved, knowing that a higher number of saved registers implies a

longer context switching time. An interesting feature available in some DSPs, such as the ADI

SHARC AD21160 [22], is the presence of two register sets, called ‘primary’ and ‘alternate’ for all the

CPU’s key registers. When an interrupt occurs, the alternate register set can be used, thus allowing a

very fast context switch. Table 6 shows the four interrupt dispatchers available on the ADSP21160M

DSP and their corresponding latency (‘Cycles before ISR’) and context restore time (‘Cycles after

ISR’. The ‘Final’ dispatcher is intended for use with user-written assembly functions or C functions

that have been compiled using ‘#pragma interrupt’. In particular, this dispatcher relies on the compiler

(or assembly routine) to save and restore all appropriate registers.

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

185

20

3.6 DSP core example: TI TMS320C67x

Figure 19 shows TI’s TMS320C6713 DSP [23] core architecture, as an example of modern VLIW

architecture implementing many of the characteristics described in Section 3. This DSP is that used in

the laboratory companion of the lectures upon which this paper is based.

Boxes inside the yellow square belong to the DSP core architecture, which here is considered to

include the cache memory as well as the DMA controller. The white boxes are components common

to all C6000 devices; grey boxes are additional features on the TMS320C6713 DSP.

Fig. 19: TI TMS320C6713 DSP core architecture. Picture courtesy of TI [23].

The TMS320C6713 DSP is a floating point DSP with VLIW architecture. The internal program

memory is structured so that a total of eight instructions can be fetched at every cycle. To give a

numerical example, with a clock rate of 225 MHz the C6713 DSP can fetch eight, 32-bit instructions

every 4.4 ns. Features of the C6713 include 264 kBytes of internal memory: 8 kB as L1 cache and

256 kB as L2 memory shared between program and data space. The processing of instructions occurs

in each of the two data paths (A and B), each of which contains four functional units (.L, .S, .M, .D).

An Enhanced DMA (EDMA) controller supports up to 16 EDMA channels. Four of the sixteen

channels (channels 8−11) are reserved for EDMA chaining, leaving twelve EDMA channels available

to service peripheral devices.

4 DSP peripherals

4.1 Introduction

The available peripherals are an important factor for the DSP choice. Peripherals are here considered

as belonging to two categories:

a) interconnect, discussed in Section 4.2;

b) services, such as timers, PLL and power management, discussed in Section 4.3.

M.E. ANGOLETTA

186

21

DSP developers must in fact carefully evaluate the needs of their system in terms of

interconnect and services required, to avoid bottlenecks and reduced system performance.

Modern DSPs often have several peripherals integrated on-chip, such as UARTs, serial, USB

and video ports. There are benefits in using embedded peripherals, such as fast performance and

reduced power consumption. There are, however, drawbacks, in that embedded peripherals can be less

flexible across applications and their unit cost might be higher.

The evolution of DSP-supported peripherals has been terrific over the last 20 years. From the

original few parallel and serial ports, DSP can now support a wide peripherals range, including those

needed by audio/video streaming applications. Often the DSP chip does not have pins to allow using

all supported peripherals at the same time. To overcome this limitation, the pins are multiplexed, i.e.,

the DSP developer must select at boot time which peripherals he/she needs to have available. An

example of pin multiplexing referred to TI’s TMS320C6713 DSP is given in Section 4.4.

An overview of interconnect and DSP services is given in Sections 4.2 and 4.3, respectively.

Hints on different interfacing possibilities to external memories and data converter memories are

provided in Sections 4.5 and 4.6, respectively. Finally, a brief outline of the DSP booting process is

given in Section 4.7.

4.2 Interconnect

The amount of supported interconnect and data I/O is huge, so only a few examples are given below,

divided per interconnect type.

Serial interfaces

a) Serial Peripheral Interface (SPI): this is an industry-standard synchronous serial link that

supports communication with multiple SPI compatible devices. The SPI peripheral is a

synchronous, four-wire interface consisting of two data pins, one device select pin, and a

gated clock pin. With the two data pins, it allows for full-duplex operation to other SPI

compatible devices. An example of DSP fitted with a SPI port is ADI’s Blackfin ADSP-

BF533 [24].

b) Multichannel Buffered Serial Ports (McBSP) [25] on TI’s DSPs: this serial interface is

based upon the standard serial port found in TMS320C2x and TMS320C5x DSPs.

c) Multichannel Audio Serial Port (McASP) [26] on TI’s DSPs: this is a serial port optimized

for the needs of multichannel audio applications. Each McASP includes transmit and

receive sections that can operate synchronized as well as completely independent, i.e., with

separate master clocks, bit clocks, and data stream formats.

Parallel interfaces

a) ADI’s linkports [27] are parallel interfaces that allow DSP–DSP as well as DSP–peripheral

connection. An example of their use for inter-DSP communication to build multi-DSP

systems is given in Sub-section 9.3.1.

b) Parallel Peripheral Interface (PPI) [28] on ADI’s Blackfin DSP: this is a multifunction

parallel interface, configurable between 8 and 16 bits in width. It supports bidirectional data

flow and it includes three synchronization lines and a clock pin for connection to an

externally-supplied clock. The PPI can receive data at clock speeds of up to 65 MHz, while

transmit rates can approach 60 MHz.

Other interfaces commonly found, for instance in TI DSPs, are Peripheral Component

Interconnect (PCI) [29], Inter-Integrated Circuit (I2C) [30], Host-Port Interface (HPI) [31] and

General-Purpose Input/Output (GPIO) [32].

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

187

22

4.3 Services

System services provide functionality that is common to embedded systems; the on-chip hardware is

generally accompanied by an API that allows one to easily interface to them. A few examples of

services are given below.

a) Timers: DSPs are typically fitted with one or more general-purpose timers that are used to

time or count events, generate interrupts to the CPU, or send synchronization events to a

DMA/EDMA controller. More information on timers for TI’s TMS320C6000 DSPs can be

found in Ref. [33].

b) PLL controller: it generates clock pulses for the DSP code and the peripherals from internal

or external clock signals. More information on PLL controllers for TI’s TMS320C6000

DSPs can be found in Ref. [34].

c) Power Management: the power-down logic allows the reduction of clocking so as to reduce

power consumption. In fact, most of the operating power of CMOS logic dissipates during

circuit switching from one logic state to the other. Significant power can be saved by

preventing some of these level switches. More information on power management logic of

TI’s TMS320C6000 DSPs can be found in Ref. [35].

d) Boot configuration: a variety of boot configurations are often available in DSPs. They are

user-programmable and determine what actions the DSP performs after it has been reset to

prepare for the initialization. These actions include loading the DSP code load from external

memory or from an external host. Some boot modes are outlined in Section 4.7. More

information on boot modes, device configuration, and available boot processes for TI

TMS320C62x/67x is available in Ref. [36].

e) JTAG: this interface implements the IEEE standard 1149.1 and allows emulation and

debugging. A detailed description of its use can be found in Section 7.2. Figure 20 shows a

typical JTAG connector and corresponding signals [37].

Fig. 20: Fourteen-pin JTAG header and corresponding signals. Picture courtesy of TI [37].

M.E. ANGOLETTA

188

23

4.4 TI C6713 DSP example

The peripherals available on TI’s TMS320C6713 DSP are shown in Fig. 21 as boxes encircled by a

yellow shape. The white boxes are components common to all C6000 devices, while grey boxes are

additional features on the TMS320C6713 DSP.

Many peripherals are available on this DSP; however, there are pins that are shared by more

than one peripheral and are internally multiplexed. Most of these pins are configured by software via a

configuration register, hence they can be programmed to switch functionality at any time. Others (such

as the HPI pins) are configured by external pullup/pulldown resistors at DSP chip reset; as a

consequence, only one peripheral has primary control of the function of these pins after reset.

Fig. 21: TI TMS320C6713 DSP available peripherals. Picture courtesy of TI [23].

4.5 Memory interfacing

DSPs often have to interface with external memory, typically shared with host processors or with other

DSPs. The two main mechanisms available to implement the memory interfacing are to use hardware

interfaces already existing on the DSP chip or to provide external hardware that carries out the

memory interfacing. These two methods are briefly mentioned below.

Hardware interfaces are often available on TI as well as on ADI DSPs. An example is TI

External Memory Interface (EMIF) [38], which is a glueless interface to memories such as SRAM,

EPROM, Flash, Synchronous Burst SRAM (SBSRAM) and Synchronous DRAM (SDRAM). On the

TMS320C6713 DSP, for instance, the EMIF provides 512 Mbytes of addressable external memory

space. Additionally, the EMIF supports memory width of 8 bits, 12 bits and 32 bits, including

read/write of both big- and little-endian devices.

When no dedicated on-chip hardware is available, the most common solution for interfacing a

DSP to an external memory is to add external hardware between memory and DSP, as shown in

Fig. 22. Typically this is done by using a CPLD or an FPGA which implements address decoding and

access arbitration. Care must be taken when programming the access priority and/or interleaved

memory access in the CPLD/FPGA. This is essential to preserve the data integrity. Synchronous

mechanisms should be preferred over asynchronous ones to carry out the data interfacing.

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

189

24

Fig. 22: Generic DSP–external memory interfacing scheme. Very often the h/w interface consists

of a CPLD or an FPGA.

4.6 Data converter interfacing

DSPs provide a variety of methods to interface with data converters such as ADCs. On-chip

peripherals are a very convenient data transfer mechanism, since data converters are typically much

slower than the DSPs they are interfaced with, hence asking the DSP core to directly retrieve data

from the converters is a waste of valuable processing time.

Serial interfaces are often available in TI’s DSPs: peripherals such as McBSP and McASP plus

the powerful DMA allow an easy interface to many data converter types [39, 40]. Another possible

solution for TI DSPs is to use the EMIF in asynchronous mode together with the DMA.

In addition to serial interfaces, ADI Blackfin DSP provides a parallel interface, namely the PPI

interface mentioned in Section 4.2, as a convenient way to interact with many converters. This

interface typically allows higher sampling rates than the serial interfaces.

A general solution for implementing the DSP–data converter interface is to use an FPGA

between DSP and converter, so as to re-buffer the data. An example of this hardware implementation

for ADI Blackfin DSPs used in wireless portable terminals is given in Ref. [41]. Additional pre-

processing, such as filtering or down-conversion, can also be carried out in the FPGA. This is the case

for instance in CERN’s LEIR LLRF system [42], where converters such as ADCs and DACs are

hosted on daughtercards. Powerful FPGAs located on the same daughtercards carry out pre-processing

and diagnostics actions under full DSP control.

Finally, mixed-signal DSPs, i.e., DSPs with embedded ADCs and/or DACs, are also available.

An example of mixed-signal DSP is ADI’s ADSP-21990, containing a pipeline flash converter with

eight independent analog inputs and sampling frequency of up to 20 MHz.

4.7 DSP booting

The actions executed by the DSP immediately after a power-down or a reset are called DSP boot and

are defined by a certain number of configurable input pins. This paragraph will focus on how the

executable file(s) is uploaded to the DSP after a power-down or reset. Two methods are available,

which typically correspond to differently built executables. More information on the code building

process and on the many file extensions can be found in Section 6.4.

The first method is to use the JTAG connector to directly upload to the executable in the DSP.

Upon a DSP power-down the code will typically not be retained in the DSP and another code upload

will be necessary. This method is used during the system debugging phase, when additional useful

information can be gathered via the JTAG.

On operational systems the DSP loads the executable code without a JTAG cable. Many

methods are available for doing this, depending on the DSP family and manufacturer; some general

ways are described below.

a) No-boot. The DSP fetches instructions directly from a pre-determined memory address,

corresponding to EPROM or Flash memory and executes them. On SHARC DSPs, for

instance, the pre-defined start address is typically 0x80 0004.

M.E. ANGOLETTA

190

25

b) Host-boot. The DSP is stalled until the host configures the DSP memory. For TI

TMS320C6xxx DSPs, for instance, this is done via the HPI interface. When all necessary

memory is initialized, the host processor takes the DSP out of the reset state by writing in a

HPI register.

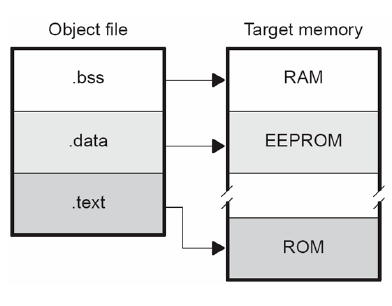

c) ROM-boot. A boot kernel is uploaded from ROM to DSP at boot time and starts executing

itself. The kernel copies data from an external ROM to the DSP by using the DMA

controller and overwrites itself with the last DMA transfer. After the transfer is completed

the DSP begins its program execution. Figure 23 visualizes the TI DSP process of booting

from ROM memory: the program (shown in green) has been moved from ROM to L2 and

L1 Program (L1P) cache via EMIF and DMA.

Fig. 23: Example of TI TMS320C6x DSP booting from ROM memory. The picture is courtesy of

TI [43].

5 Real-time design flow: introduction

Figure 24 shows a time-ordered view of the various activities or phases that a real-time system

developer may be required to carry out during a new system development. These activities will be

treated in this document in a didactic rather than in a time-related order, to allow even the un-

experienced reader to build up the knowledge needed at each step. It should be underlined that the

real-time design flow may be not totally forward-directed, and at each step the developer may have to

go back to a previous phase to make modifications or carry out additional tests.

Fig. 24: Activities typically required to develop a new, DSP-based system

The ‘system design’ phase may include both hardware and software design. For hardware

design, the developer must make choices such as the DSP type to use, the hardware

architecture/interfaces, and so on. For software design, choices such as the code structure, the data

flow and data exchange interfaces must be made. This phase is treated in Section 9.

The ‘software development’ phase includes creating the DSP project and writing the actual DSP

code. Basic and essential information for this phase is given in Section 6.

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

191

26

The ‘debug’ phase is a very critical one, where the developer must verify that the code executes

what it was meant to. Some debugging techniques as well as different methodologies available (such

as simulation and emulation) are described in Section 7.

The ‘analysis and optimization’ phase allows the developer to optimize the system for different

goals, such as speed, memory, input/output bandwidth, or power consumption. Analysis and

optimization tools are described in Section 8, together with some optimization guidelines.

Finally, the ‘system integration’ is the essential phase where the system is integrated within the

existing infrastructure and is therefore made fully operational. It is not possible to give precise details

on this phase owing to the many existing control infrastructures. However, general guidelines and

good practices are discussed in Section 10.

6 Real-time design flow: software development

DSPs are programmed by software via a cross-compilation. This means that the executable is created

in a platform (such as a Windows- or a SUN-based machine) different from the one that it runs on, i.e.,

the DSP itself. One reason for this is that DSPs have limited and dedicated resources, hence it would

not be convenient or even possible to run a file system with a user-friendly development environment.

The choice of programming languages is vast, including native assembly language as well as

high-level languages such as C, C++, C extensions and dialects, Ada and so on. High-level software

tools such as MATLAB and National Instruments allow one to automatically generate code files from

graphical interfaces, thus providing rapid prototyping methods.

The code-building tools are very often provided by the DSP manufacturers themselves.

Compilers and Integrated Development Environments (IDEs) are also available from other sources,

such as Green Hills Software. The trend is now towards more powerful and user-friendly tools,

capable of taming and using in the best possible way the underlying hardware and software

complexity.

6.1 Development set-up and environment

DSP executables are developed by using Integrated Development Environments (IDEs) provided by

DSP manufacturers; they integrate many functions, such as editing, debugging, project files

management, and profiling. Very often the licences are bought on a ‘per-project’ basis, even if ADI

provides also floating (i.e., networked) licences. The development environment for TI and ADI DSPs

are called ‘Code Composer Studio’ and ‘VisualDSP++’, respectively; they provide very similar

functionalities. It should be underlined that TI has recently made available free of charge the compiler,

assembler, optimizer and linker to non-commercial users. However, neither the IDE nor a debugger

were included, thus the developer must still use the proprietary tools.

Figure 25 gives an example of a typical Code Composer screen. On the left-hand side there is

the list of all files included in the software project. At the centre of the screen two windows show the

code, as a C file (process.c) and as assembly code (Dis-assembly window). A breakpoint has been set

and the execution is stopped there. Below the code windows, two memory windows are also visible,

detailing the data present at addresses 0x80000000 and following, and at addresses 0x40000030 and

following. Data at address 0x80000002 is of a different colour because its value changed recently. At

the bottom of the IDE screen the following item are displayed: a) the Compile/Link window, which

details the results from the last code compilation; b) the Watch window, which displays the value

assumed by two C-language variables and c) the Register window, which details the contents of all

DSP registers. On the right-hand side there are three graphs: the yellow ones show memory regions,

while the green one shows the Fast Fourier Transform of data stored in memory as calculated by the

M.E. ANGOLETTA

192

27

IDE. The reader can find more details about Code Composer Studio and its capabilities in

Refs. [44]–[46].

Fig. 25: Screenshot from Code Composer, i.e., the TI DSP IDE. The picture was taken in 1998

from the development of CERN’s AD Schottky system.

Figure 26 shows a typical DSP-based system set-up. On the left-hand side the DSP IDE runs on

a PC, which is connected to the DSP via a JTAG emulator and pod. This allows one to edit the code,

compile it, download it to the hardware and retrieve debug information. On the right-hand side the

system exploitation is shown whereby the DSP runs its program and a PowerPC board, running

LynxOS and acting as master VME, controls the DSP actions, downloads the control parameters, and

retrieves the resulting data. The example shown is that of CERN’s AD Schottky measurement

system [47].

Fig. 26: Typical system exploitation (on the left-hand side) and code development (on the right-

hand side) set-ups

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

193

28

6.2 Languages: assembly, C, C++, graphical

The choice of the language(s) to be used for the DSP development is very important and depends

mainly on the selected DSP, as different DSPs may support different languages. Often a DSP system

will include both assembly and high-level languages; the language choice or the chosen balance

between the languages depends also on the required processor workload, i.e., on how much the code

should be optimized to satisfy the requirements. The language choice is nowadays much larger than in

the past, mainly thanks to the improvements of compilers. Additionally, the increased complexity of

DSP hardware (see Section 3), such as deep pipelining, makes the hand-optimization much more

difficult. The main language choices include: a) assembly language; b) high-level languages such as C,

C dialects/extensions and C++; c) graphical languages such as Matlab. These three choices are

discussed below.

6.2.1 Assembly language

The assembly language is very close to the hardware, as it explicitly works with registers and it

requires a detailed knowledge of the inner DSP architecture. To write assembly code typically takes

longer than to write high-level languages; additionally, it is often more difficult to understand other

people’s assembly programs than to understand programs written in high-level languages. The

assembly grammar/style and the available instruction set/peripherals depend not only on the DSP

manufacture, but also on the DSP family and on the targeted DSP. As a consequence, it might be

difficult or even impossible to port assembly programs from one DSP to another. For instance, for

DSPs belonging to the TI C6xxx family there is about an 85% assembly code compatibility, i.e., when

going from a C62x to a C64x DSP there are no issues but if moving from a C64x to a C62x one might

have to introduce some changes in the code owing to the different instruction set.

DSP applications have typically very demanding processing requirements. The need to obtain

the maximum processing performance has often led DSP programmers to use assembly programming

extensively. Nowadays the improvements in code compilers and the increasing difficulty in hand-

optimizing assembly code have prompted DSP developers to use high-level languages more often.

However, in some DSPs there are still features available only in assembly, such as the super-fast

interrupt dispatcher for ADI’s ADSP21160M DSP shown in Table 6. Very often, the bulk of the DSP

code is written in high-level languages and the parts needing a better performance may be written in

assembly.

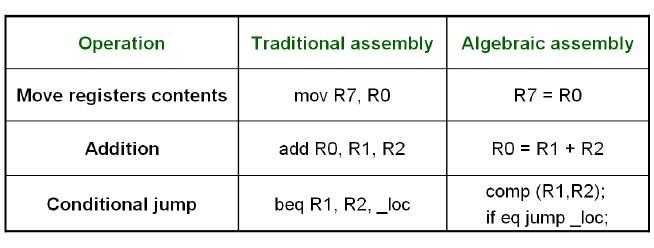

Different manufacturers adopt different assembly styles, which have also evolved over the

years. Table 7 shows a comparison between a traditional assembly style, adopted for instance by TI

C40 DSPs, and the algebraic assembly, adopted by ADI SHARC DSPs.

Table 7: Comparison of assembly code styles. The traditional assembly style was adopted for instance by TI

TMC320C4x DSPs, while the algebraic assembly is used in ADI.

M.E. ANGOLETTA

194

29

Figure 27 gives an example of how one line of C code is converted to the corresponding

assembly code for the TI C6317 DSP. The upper window shows part of the ‘SIN_to_output_RTDX.c’

file, which was included in the DSP laboratory companion of the lectures described in this document;

the lower ‘Disassembly’ window shows the resulting assembly code.

Fig. 27: C and assembly language examples for the TI C6713 DSP. Window (a): C source code.

Window (b): assembly code resulting from the first C-code line in window (a).

6.2.2 High-level languages: C

The C language was developed in the early 1970s; three main standards exist, referred to as ANSI,

ISO, and C99 respectively. There are many reasons why it is convenient to use the C language in DSP-

based systems. The C language is very popular and known by engineers and software developers alike;

it is typically easier to understand and faster to develop than assembly code. It supports features useful

for embedded systems such as control structures and low-level bit manipulations. All DSPs are

provided with a C compiler, hence it may be possible to port the C code from one DSP to another.

There are, however, drawbacks to the use of standard C languages in DSP-based systems. First,

the executable resulting from a C-language source code is typically slower than that derived from

optimized assembly code and has a larger size. The ANSI/ISO C language does not have support for

typical DSP hardware features such as circular buffers or non-flat memory spaces. Additionally, the

address at which data must be aligned can vary between different DSP architectures: on some DSPs a

4-byte integer can start at any address, but on other DSPs it could start for instance at even addresses

only. As a consequence, the data alignment obtained with ANSI/ISO C compilers may be

incompatible with the data alignment required by the DSP, thus leading to deadly bus errors. In the

standard C language there is no native support for fixed-point fractional variables, a serious drawback

for many DSPs and signal processing algorithms. Finally, the standard C compiler data-type sizes are

not standardized and may not fit the DSP native data size, leading for instance to the replacement of

fast hardware implementations with slower software emulations. For instance, 64-bit double

operations are available in ADI’s TigerSHARC as software emulations only; hence the declaration of

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

195

30

variables as double and not as float will result in slower execution. Table 8 shows how data-type sizes

can vary for different DSPs.

Table 8: Examples of data-type size for different DSPs

Table 9 shows the data-type sizes and number format for the TI C6713 DSP. The 2’s

complement and binary formats are used for signed and unsigned numbers, respectively.

Table 9: Data-type sizes and number format for the TI C6713 DSP

There are two main approaches to adapting the C language to specific DSPs hardware and to the

needs of signal processing applications. The first approach is the definition of ‘intrinsic’ functions, i.e.,

of functions that map directly to optimized DSP instructions. Table 10 shows some examples of

intrinsic functions available in TI C6713 DSPs. The second approach is to ‘extend’ the C-language so

as to include specialized data types and constructs. Of course, the drawback of the latter approach is a

reduced portability of the resulting C language.

Table 10: TI C6713 intrinsic functions – some examples.

M.E. ANGOLETTA

196

31

6.2.3 High-level languages: C++

The C++ programming language supports object-oriented programming and is the language of choice

for many business computer applications. C++ compilers are often available for DSPs; some

advantages of using it are the ability to provide a higher abstraction layer and the upwards

compatibility with the C language. There are, however, several disadvantages, for instance the

increased memory requirements due to the more general constructs. Additionally, many application

programs and libraries rely on functions such as malloc() and free(), which need a heap.

While the way to adapt the C-language to DSPs is to add features, the C++ language is adapted

by trimming its features. C++ characteristics typically removed are multiple inheritance and exception

handling; the resulting code is more efficient and the executable is smaller.

6.2.4 Graphical languages

A trend which has developed over the last five to ten years is to use graphical programming to

generate DSP code. Examples of programs and tools aimed at this are the MATLAB, Hypersignal

RIDE (now acquired by National Instruments) and the LabVIEW DSP Module. These methodologies

generate DSP executables that often are not highly optimized, therefore not suitable for the

implementation of demanding DSP-based systems. However, they allow one to quickly move from the

design to the implementation phase, thus providing a rapid prototyping methodology.

Fig. 28: MATLAB graphical programming used in the DSP laboratory companion in these notes.

The digital filter block can easily be set up by using a user-friendly set-up GUI.

As an example, MATLAB provides tools such as Simulink, Real-Time Workshop, Real-Time

Workshop Embedded Coder, Embedded Target for TI C6xxx DSPs and Link for Code Composer that

allow generating embedded code for TI DSPs and downloading it directly into a DSP evaluation

DIGITAL SIGNAL PROCESSOR FUNDAMENTALS AND SYSTEM DESIGN

197

32

board. These tools provide interfaces for the DSP peripherals, too. The DSP laboratory companion on

these notes was based upon TI C6713 DSK and MATLAB tools. Figure 28 shows the MATLAB

graphical program that constituted one of the laboratory exercises. MATLAB allows not only to

interface immediately with the on-board CODEC by using the ADC and DAC blocks, but also to set

up through a user-friendly GUI the digital filter to be implemented.

6.3 Real-time operating system

A Real-Time Operating System (RTOS) is a program that has real-time capabilities, is downloaded to

the DSP at boot time, and manages all DSP programs, typically referred to as tasks. The RTOS

interfaces tasks with peripherals such as DMA, I/O and memory, via an Application Program Interface

(API), as shown in Fig. 29.

Fig. 29: Embedded DSP software components

A RTOS is typically task-based and supports multiple tasks (often referred to as threads) by

time-sharing, i.e., by multiplexing the processor time over the active tasks set. Each task has a priority

associated to it and the RTOS schedules which task should run depending on the priority. Very often

this is done in a pre-emptive way, meaning that when a high-priority task becomes ready for

execution, it pre-empts the execution of a lower-priority task, without having to wait for its turn in the

regular re-scheduling. Finally, RTOS have a small memory footprint, so as not to have too negative an

impact on the DSP executable size.

There are many advantages when using a RTOS to develop a DSP-based system. For instance,

the API and library shown in Fig. 29 provide a device abstraction level between DSP hardware